# Combinatorial Register Allocation and Instruction Scheduling

ROBERTO CASTAÑEDA LOZANO, RISE SICS, Sweden and KTH Royal Institute of Technology, Sweden

MATS CARLSSON, RISE SICS, Sweden

GABRIEL HJORT BLINDELL, KTH Royal Institute of Technology, Sweden

CHRISTIAN SCHULTE, KTH Royal Institute of Technology, Sweden and RISE SICS, Sweden

This paper introduces a combinatorial optimization approach to register allocation and instruction scheduling, two central compiler problems. Combinatorial optimization has the potential to solve these problems optimally and to exploit processor-specific features readily. Our approach is the first to leverage this potential *in practice*: it captures the *complete* set of program transformations used in state-of-the-art compilers, *scales* to medium-sized functions of up to 1000 instructions, and generates *executable* code. This level of practicality is reached by using constraint programming, a particularly suitable combinatorial optimization technique. Unison, the implementation of our approach, is open source, used in industry, and integrated with the LLVM toolchain.

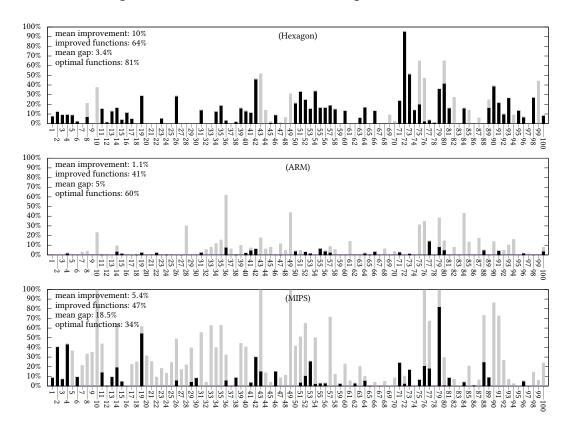

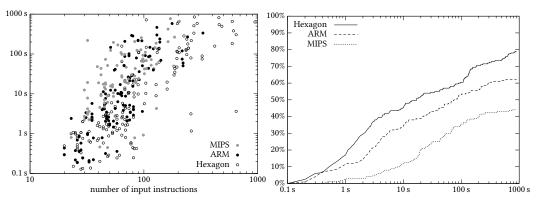

An extensive evaluation confirms that Unison generates better code than LLVM while scaling to mediumsized functions. The evaluation uses systematically selected benchmarks from MediaBench and SPEC CPU2006 and different processor architectures (Hexagon, ARM, MIPS). Mean estimated speedup ranges from 1.1% to 10% and mean code size reduction ranges from 1.3% to 3.8% for the different architectures. A significant part of this improvement is due to the integrated nature of the approach. Executing the generated code on Hexagon confirms that the estimated speedup results in actual speedup. Given a fixed time limit, Unison solves optimally functions of up to 946 instructions, nearly an order of magnitude larger than previous approaches.

The results show that our combinatorial approach can be applied in practice to trade compilation time for code quality beyond the usual compiler optimization levels, identify improvement opportunities in heuristic algorithms, and fully exploit processor-specific features.

$\label{eq:ccs} \textbf{CCS Concepts: } \bullet \textbf{Computing methodologies} \to \textbf{Discrete space search}; \textit{Planning and scheduling}; \bullet \textbf{Software and its engineering} \to \textbf{Compilers}; \textit{Constraint and logic languages}.$

Additional Key Words and Phrases: combinatorial optimization; register allocation; instruction scheduling

# 1 INTRODUCTION

Register allocation and instruction scheduling are central compiler problems. Register allocation maps temporaries (program or compiler-generated variables) to registers or memory. Instruction scheduling reorders instructions to improve total latency or throughput. Both problems are key to generating high-quality assembly code, are computationally complex (NP-hard), and are mutually

This paper is partially based on preliminary work presented at the *Principles and Practice of Constraint Programming* (2012) [20]; *Languages, Compilers, and Tools for Embedded Systems* (2014) [21]; and *Compiler Construction* (2016) [22] conferences. Compared to the preliminary work, this paper is completely restructured and rewritten, completes the combinatorial model with rematerialization, proposes extensions to capture additional program transformations and processor-specific features, and contributes a more exhaustive evaluation. Additions to the evaluation include more benchmarks and processors, evidence of the fundamental benefit of the integrated approach, an in-depth study of scalability, and actual execution measurements.

Authors' addresses: Roberto Castañeda Lozano, RISE SICS, Electrum 229, Kista, 164 40, Sweden, KTH Royal Institute of Technology, School of Electrical Engineering and Computer Science, Electrum 229, Kista, 164 40, Sweden, roberto. castaneda@ri.se; Mats Carlsson, RISE SICS, Electrum 229, Kista, 164 40, Sweden, mats.carlsson@ri.se; Gabriel Hjort Blindell, KTH Royal Institute of Technology, School of Electrical Engineering and Computer Science, Electrum 229, Kista, 164 40, Sweden, ghb@kth.se; Christian Schulte, KTH Royal Institute of Technology, School of Electrical Engineering and Computer Science, Electrum 229, Kista, 164 40, Sweden, RISE SICS, Electrum 229, Kista, 164 40, Sweden, cschulte@kth.se.

interdependent: no matter in which order these problems are approached, aggressively solving one of them might worsen the outcome of the other [45, 47, 49, 74].

Today's compilers typically solve each problem in isolation with heuristic algorithms, taking a sequence of greedy decisions based on local optimization criteria. This arrangement reduces compilation time but precludes optimal solutions and complicates the exploitation of processor-specific features.

Combinatorial optimization has been proposed to address these limitations: it can deliver optimal solutions according to a model, it can accurately capture problem interdependencies, and it can accommodate specific architectural features at the expense of increased compilation time [24]. While this approach shows promise for register allocation and instruction scheduling, its practical significance has not yet been established. Typically, combinatorial approaches model only a subset of the program transformations offered by their heuristic counterparts, do not scale beyond small problems of up to 100 input instructions, and are not known to generate executable code.

The goal of this paper is to introduce a combinatorial approach to integrated register allocation and instruction scheduling that is practical. By *practical* we mean that the approach is:

**Complete.** It models the same set of program transformations as state-of-the-art compilers. **Scalable.** It scales to medium-sized problems of up to 1000 input instructions.

**Executable.** It generates executable code.

This combination of properties allows us, for the first time, to evaluate the potential benefit of combinatorial register allocation and instruction scheduling in practice: completeness enables a direct comparison with heuristic approaches; scalability puts most problems from typical benchmark suites within reach; and executability is a precondition to study the practical significance. Our evaluation shows that this potential benefit can be achieved, generating better code than state-of-the-art heuristic approaches for a variety of benchmarks, processors, and optimization goals.

Our approach has practical applications for both compiler users and developers, as corroborated by our research partner Ericsson [98]. Compiler users can apply it to trade compilation time for code quality beyond the usual compiler optimization levels. This is particularly attractive if longer compilation times are tolerable, such as for compilation of high-quality library releases or embedded systems software [53]. If compilation time is more limited, our approach might still be applied to the most frequently executed parts of a program. Compiler developers can apply the combinatorial approach as a baseline for assessment and development of heuristic approaches, exploiting the optimal, integrated nature of its solutions. Furthermore, comparing the generated code can reveal improvement opportunities in heuristic algorithms, even for production-quality compilers such as LLVM [18]. Another application is to generate high-quality code for processor-specific, irregular features. Such features can be naturally modeled and fully exploited by combinatorial approaches, while adapting heuristic approaches tends to involve a major effort [62]. The ease of modeling of our approach can also be exploited for rapid compiler prototyping for new processor revisions.

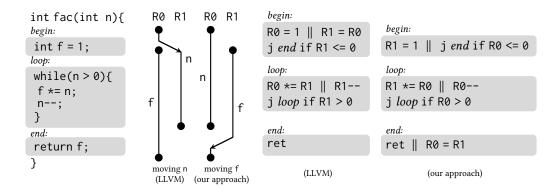

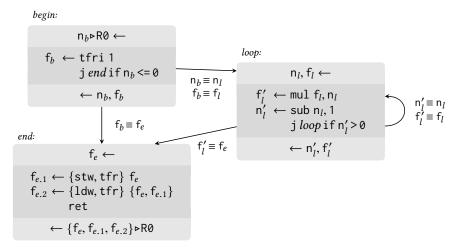

**Example 1.** Figure 1 illustrates our combinatorial approach in practice [17]. Figure 1a shows a C implementation of the factorial function. The function takes n as argument, initializes f to one, iterates multiplying and accumulating f with n in each iteration until n is zero, and returns f.

Register allocation for this function must assign n and f to different registers within the *loop* basic block, since their values would be otherwise clobbered (that is, mutually overwritten). Let us assume that the target processor is Hexagon, a multiple-issue digital signal processor ubiquitous in modern mobile platforms [30]. Its calling convention forces the assignment of n and f to the same register (R0) on entry and on return respectively [80]. These clobbering and calling convention constraints can only be satisfied by assigning one of the program variables  $v \in \{n, f\}$  to some other

- (a) Factorial in C.

- (b) Register assignment.

- (c) Simplified assembly code.

Fig. 1. Motivating example: Hexagon assembly code generated by LLVM and our approach for factorial.

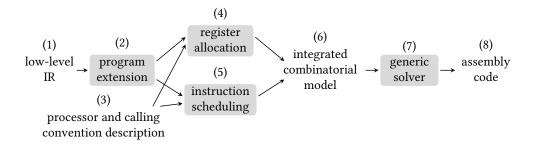

Fig. 2. Our approach to combinatorial register allocation and instruction scheduling.

register than R0 within loop and moving v to or from R0 outside of loop with a register-to-register move instruction.

Figure 1b shows how the state-of-the-art heuristic compiler LLVM [59] and our approach produce opposite assignments by moving either n or f. From an isolated register allocation perspective, both assignments incur the same cost: an additional move instruction at *begin* (LLVM) or *end* (our approach) is required. However, our integrated approach properly reflects that only the move of f can be parallelized (||) with another instruction (ret), yielding slightly faster assembly code (Figure 1c). This advanced optimization level requires reasoning about multiple aspects of global register allocation and instruction scheduling in integration.

Approach. Our approach is outlined in Figure 2. A low-level intermediate representation (IR) of a function with instructions from a specific processor is taken as input (1). The representation of the function is extended (2) to expose its structure and the multiple decisions involved in the problem. From the extended function and a description of the processor and calling convention (3), combinatorial models of register allocation (4) and instruction scheduling (5) are derived. A combinatorial model consists of variables representing the problem decisions, program and processor constraints over the variables, and an objective function to be optimized. Both models are then integrated into a single model (6) that precisely captures the interdependencies between the corresponding

4

problems. Solving the model with a generic solver (7) gives a register allocation and an instruction schedule used to generate executable assembly code (8).

A combinatorial model is of limited practical value unless complemented with suitable solving techniques, effective solving methods, and a robust implementation that gives confidence in the results. Our approach is implemented in *Unison* [23], a software tool that uses constraint programming [83] as a modern combinatorial optimization technique. Constraint programming is particularly capable of exploiting the structure underlying the register allocation and instruction scheduling problems. Unison applies general and problem-specific constraint solving methods with which medium-sized functions can be solved optimally. It also deals with the practicalities of generating executable code (such as calling convention and call stack management), delegating decisions that are interdependent with register allocation and instruction scheduling to the combinatorial model. Unison is a robust tool whose results can be used with confidence: it is open source, well-documented, systematically tested, used in industry, and integrated with the LLVM toolchain.

*Contributions.* This paper contributes the first combinatorial approach to register allocation and instruction scheduling that is *complete*, *scales* up to medium-sized problems, and generates *executable* code.

The combinatorial model is *complete* as it includes spilling (internalized into the model), register assignment and packing, coalescing, load-store optimization, live range splitting, rematerialization, and multi-allocation. This is enabled by a novel combination of abstractions that capture different aspects of register allocation together with a suitable program representation. In addition, the paper introduces model extensions for features such as stack frame elimination, latencies across basic blocks, operand forwarding, and two-address instructions.

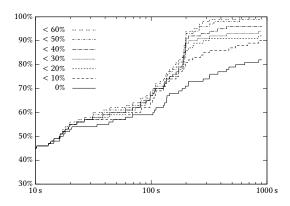

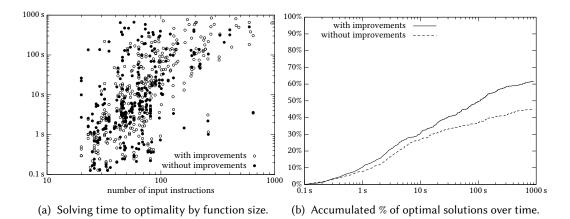

The paper introduces solving methods that are crucial for *scalability*. Extensive experiments on MediaBench [61] and SPEC CPU2006 [90] functions for three different processor architectures (Hexagon, ARM, MIPS) show that, given a time limit of 15 minutes, our approach solves optimally functions of up to 946 instructions. Under this time limit, the percentage of functions solved optimally ranges from 44% to 79% across processors, and 90% of the functions on Hexagon are solved optimally or less than 10% away from the optimal solution.

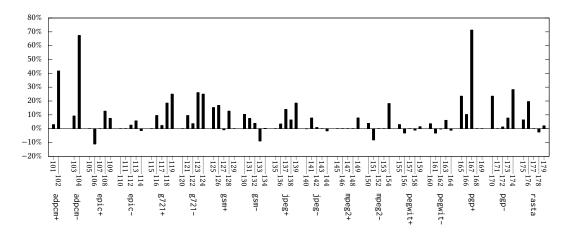

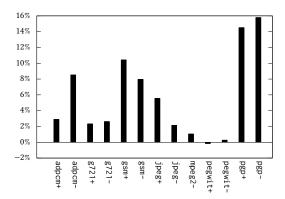

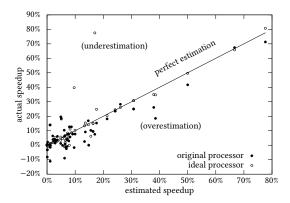

The experiments confirm that there is a potential benefit to be gained by solving register allocation and instruction scheduling in integration. Our approach exploits this potential, delivering a mean estimated speedup over LLVM ranging from 1.1% to 10% and a mean code size reduction ranging from 1.3% to 3.8%, depending on the characteristics of the processor. For the first time, the speedup estimation is examined by *executing* MediaBench applications on Hexagon, the processor with highest estimated speedup in the experiments. The results show that the approach achieves significant speedup in practice (6.6% across functions and 5.6% across whole applications).

*Plan of the paper.* Section 2 covers the background on register allocation, instruction scheduling, and combinatorial optimization. Section 3 reviews related approaches.

Sections 4-9 introduce the combinatorial model and its associated program representation. They incrementally describe local register allocation (Section 4), global register allocation (Section 5), instruction scheduling (Section 6), the integrated model (Section 7), its objective function (Section 8), and additional program transformations (Section 9). Appendix A complements this incremental description with a summary of the parameters, variables, constraints, and objective function in the combinatorial model.

Section 10 outlines the solving methods employed by Unison. Section 11 presents the experimental evaluation, where Appendix B studies the accuracy of the speedup estimation and Appendix C describes the functions used in the evaluation. Section 12 concludes and proposes future work.

#### 2 BACKGROUND

This section reviews the input program representation assumed in the paper, the register allocation and instruction scheduling problems, and constraint programming as the key technique for modeling and solving register allocation and instruction scheduling.

## 2.1 Input Program Representation

This paper assumes as input a function represented by its control-flow graph (CFG), with instructions for a specific processor already selected. Instructions *define* (assign) and *use* (access) program and compiler-generated variables. These variables are referred to as *temporaries* and are associated with a bit-width derived from their source data type.

Program points are locations between consecutive instructions. A temporary t defined by an instruction i is live at a program point if t holds a value that might be used later by another instruction j. In this situation, instruction j is said to be dependent on i. A temporary t is live-in (live-out) in a basic block b if t is live at the entry (exit) of b. The live range of a temporary t is the set of program points where t is live. Two temporaries interfere if their live ranges are not disjoint.

The paper assumes that all temporaries that are live-in into the function (such as function arguments) are defined by a *virtual entry instruction* at the entry basic block. Similarly, *virtual exit instructions* use temporaries that are live-out at the exit basic blocks of the function. *Virtual* (as opposed to *real*) instructions are pseudo-instructions introduced to support compilation and do not appear in the generated assembly code. Temporaries being live-in into the function and live-out of the function are pre-assigned according to the calling convention. A pre-assignment of a temporary t to a register r is denoted as  $t \triangleright r$ .

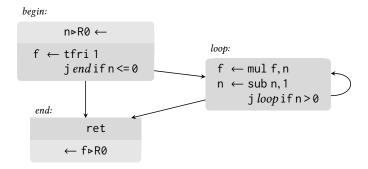

**Example 2.** Figure 3 shows the CFG from Example 1 with Hexagon instructions. For readability, Hexagon immediate transfer (tfri), conditional jump (j if), multiply (mul), subtract (sub), and jump to return address (ret) instructions are shown in simplified syntax. The body of a basic block is shown in dark gray while the boundaries containing entry and exit instructions are shown in light gray. For simplicity, *critical edges* (arcs from basic blocks with multiple successors to basic blocks with multiple predecessors) are preserved in the example CFG. In practice, such edges are often split by earlier compiler transformations.

The 32-bit temporaries n and f correspond to the int variables in Example 1. n is live-in and hence defined by the entry instruction in the begin basic block. f is live-out and hence used by the exit instruction in the end basic block. Hexagon's calling convention requires the pre-assignment n>R0 on the function's entry, and f>R0 on the function's exit. The live range of n starts with its definition by the entry instruction in the begin basic block and spans the entire loop basic block. The live range of f starts with its definition by tfri in the begin basic block and extends until the exit instruction in the end basic block. n and f interfere as their live ranges are not disjoint.

# 2.2 Register Allocation

Register allocation maps temporaries to either processor registers or memory. While processor registers have shorter access times, they are limited in number. This shortage of registers leads to a high *register pressure* for functions where many temporaries interfere. In the worst case, this may force the allocation (spilling) of some of the temporaries to memory. The spill of a temporary t is implemented by inserting code (often costly store and load instructions) to move t's value to and from memory. In its most basic form (called spill-everywhere),  $spill\ code$  is generated by inserting store instructions after each definition of t and load instructions before each use of t.

Register allocation applies a number of program transformations to reduce register pressure, spilling, or — if the latter is unavoidable — the overhead of the spill code:

Fig. 3. CFG of the factorial function with Hexagon instructions.

**Register assignment** maps non-spilled temporaries to individual registers, reducing register pressure by reusing registers among non-interfering temporaries.

**Live range splitting** allocates temporaries to different locations in different parts of their live ranges.

**Coalescing** allocates a temporary's split live range to the same location to eliminate the corresponding copy instructions (dual of live range splitting).

**Load-store optimization** avoids reloading spilled values by reusing values loaded in previous parts of the spill code.

**Multi-allocation** allocates temporaries simultaneously to registers as well as memory, reducing the overhead of spilling in certain scenarios [31].

**Register packing** assigns temporaries of small bit-widths to different parts of larger-width registers (for processors supporting such assignments) to improve register utilization.

**Rematerialization** recomputes values at their use points rather than spilling them when the recomputation instructions are deemed less costly than the spill code.

*Scope.* Register allocation can be solved locally or globally. *Local* register allocation handles single basic blocks, spilling all temporaries that are live across basic block boundaries. *Global* register allocation handles entire functions, potentially improving code quality by keeping temporaries in registers across basic block boundaries.

Calling convention management. Register allocation is responsible to enforce the pre-assignment of arguments and return values to certain registers and the preservation of callee-saved registers across function calls as dictated by the calling convention. A common approach to handle callee-saved registers is to hold their values in temporaries that are live through the entire function and that can be spilled at the function's entry and exit. This approach can be refined by moving the spill code closer to the program points where the callee-saved registers are needed (shrink-wrapping [27]).

SSA-based register allocation. Static single assignment (SSA) [34] is a program form in which temporaries are defined exactly once. This form is useful for register allocation as it allows register assignment to be solved optimally in polynomial time [48]. SSA places  $\phi$ -functions of the form  $t_n \leftarrow \phi$   $(t_1, t_2, \ldots, t_{n-1})$  at the entry of basic blocks with multiple incoming arcs to distinguish which definition among  $\{t_1, t_2, \ldots, t_{n-1}\}$  reaches  $t_n$  depending on the program execution. Temporaries related transitively by  $\phi$ -functions are called  $\phi$ -congruent [92]. This paper uses a generalized form of SSA for global register allocation, as Section 5.1 explains.

# 2.3 Instruction Scheduling

Instruction scheduling assigns issue cycles to program instructions. Valid instruction schedules must satisfy instruction dependencies and constraints imposed by limited processor resources.

Latency. Dependencies between instructions are often associated with a latency indicating the minimum number of cycles that must elapse between the issue of the depending instructions. Variable latencies (such as those arising from cache memory accesses) are typically handled by assuming the best case and relying on the processor to stall the execution otherwise [47].

Resources. The organization of hardware resources varies heavily among different processors and has a profound impact on the complexity of instruction scheduling. This paper assumes a resource model where each resource s has a capacity cap(s) and each instruction i consumes con(i, s) units of each resource s during dur(i, s) cycles. This model is sufficiently general to capture the resources of the processors studied in this paper, including Very Long Instruction Word (VLIW) processors such as Hexagon that can issue multiple instructions in each cycle. These processors can be modeled by an additional resource with capacity equal to the processor's issue width.

*Order.* Non-integrated compilers perform instruction scheduling before or after register allocation. Pre-register-allocation scheduling typically seeks a schedule that reduces register pressure during register allocation, while post-register-allocation scheduling often aims at minimizing the duration of the schedule. The latter is particularly relevant for *in-order* processors which issue instructions according to the schedule produced by the compiler, although *out-of-order* processors can also benefit from compile-time instruction scheduling [47].

*Scope.* Instruction scheduling can be solved at different program scopes. This paper is concerned with *local* instruction scheduling, where the instructions from each basic block are scheduled independently. Larger scopes to which instruction scheduling can be applied include *superblocks* (consecutive basic blocks with multiple exit points but a single entry point) and *loops* (where the instructions of multiple iterations are scheduled simultaneously in a pipelined fashion).

# 2.4 Constraint Programming

Combinatorial optimization is a collection of techniques to solve computationally hard combinatorial optimization problems such as register allocation and instruction scheduling. Examples of these techniques are constraint programming (CP) [83], integer programming (IP) [75], Boolean satisfiability (SAT) [12], partitioned Boolean quadratic programming (PBQP) [85], and dynamic programming (DP) [33]. Their key property is *completeness*: they automatically explore the full solution space and, given enough time, guarantee to find the optimal solution if there is one.

Combinatorial optimization techniques capture the problems to be solved as combinatorial models. A combinatorial model consists of *variables* capturing problem decisions, *constraints* expressing relations over the variables that must be satisfied by a solution, and an *objective function* to be minimized (or maximized) expressed in terms of the variables. A *solution* to the model is an assignment of values to the variables that satisfies all the constraints, and an *optimal solution* minimizes the value of the objective function. In this paper variables are written in bold (e.g.  $\mathbf{x}$ ), and indexable variables are written as  $\mathbf{x}(i)$ .

Combinatorial optimization techniques differ significantly in the level of abstraction of their models, underlying solving methods, and problem classes for which they are particularly well-suited. This paper uses CP as a technique that is particularly suitable for handling register allocation and instruction scheduling problems. In CP, variables usually range over finite subsets of the integers or Booleans, and constraints and objective function are expressed by general relations. The purpose

of this section is to provide enough information so that the models developed in Sections 4-9 are understandable. Some additional modeling and solving methods are presented in Section 10.

Constraint solvers proceed by interleaving *constraint propagation* and *branch-and-bound search*. Constraint propagation discards value assignments that cannot be part of a solution to reduce the search space. Constraint propagation is applied iteratively until no more value assignments can be discarded [11]. If several values can still be assigned to a variable, search is used to decompose the problem into alternative subproblems on which propagation and search are repeated. Solutions found during solving are exploited in a branch-and-bound fashion to further reduce the search space [93]: after a solution is found, constraints are added such that the next solution must be better according to the objective function.

As is common in combinatorial optimization, constraint solvers are usually run with a time limit as it can be prohibitive to find the optimal solution to large problems. Constraint solvers exhibit *anytime behavior* in that they can often deliver suboptimal solutions if they time out. Even when no solution is delivered, the solvers always provide the *optimality gap* (hereafter just *gap*), an upper bound on the distance to the optimal solution. The gap can be used as an estimation of the computational effort to obtain the optimal solution, as a certificate of the quality of suboptimal solutions, or as a criterion for solver termination.

Global constraints. A key feature of CP is the use of global constraints that capture recurring modeling substructures involving multiple variables. Besides being convenient for modeling, global constraints are essential for efficient solving since they are implemented by dedicated propagation algorithms that further reduce the search space [95]. The model introduced in this paper (Sections 4-9) uses the following three global constraints:

• cumulative  $(\{\langle \mathbf{s}(i), \mathbf{d}(i), \mathbf{c}(i) \rangle : i \in (1, n)\}, b)$  ensures that a set of n tasks does not exceed a given resource capacity b, where each task i is defined by its start time  $\mathbf{s}(i)$ , duration  $\mathbf{d}(i)$ , and resource units consumed  $\mathbf{c}(i)$  [1]:

$$\sum_{i \in (1,n): \mathbf{s}(i) \le k \land \mathbf{s}(i) + \mathbf{d}(i) > k} \mathbf{c}(i) \le b \quad \forall k \in \mathbb{Z}.$$

(1)

• no-overlap ( $\{\langle \mathbf{l}(i), \mathbf{r}(i), \mathbf{t}(i), \mathbf{b}(i) \rangle : i \in (1, n)\}$ ) (also known as diffn) ensures that a set of n rectangles does not overlap, where each rectangle i is defined by its left  $\mathbf{l}(i)$ , right  $\mathbf{r}(i)$ , top  $\mathbf{t}(i)$ , and bottom  $\mathbf{b}(i)$  coordinates [10]:

$$\mathbf{r}(i) \le \mathbf{l}(j) \lor \mathbf{l}(i) \ge \mathbf{r}(j) \lor \mathbf{b}(i) \le \mathbf{t}(j) \lor \mathbf{t}(i) \ge \mathbf{b}(j) \quad \forall i, j \in (1, n) : i \ne j. \tag{2}$$

• element  $(\mathbf{x}, a, \mathbf{y})$  generalizes array access to variables by ensuring that the variable  $\mathbf{y}$  is equal to the  $\mathbf{x}^{\text{th}}$  element of an array a of integers or integer variables [94]:

$$a[\mathbf{x}] = \mathbf{y}.\tag{3}$$

As a compromise between readability and precision, the rest of the paper expresses this constraint using the array notation. This can be extended to multi-dimensional arrays provided that only a single integer variable is used for indexing. Constraints using lookup functions, such as  $f(\mathbf{x}) = \mathbf{y}$ , can be expressed as  $f[\mathbf{x}] = \mathbf{y}$  by converting f into an array. Using this constraint, we can also implement the constraint

$$\mathbf{y} \in a[\mathbf{x}] \tag{4}$$

by introducing, for each such constraint, a new array b of integer variables, where each integer variable b[i] has a domain equal to a[i], and enforcing  $b[\mathbf{x}] = \mathbf{y}$ .

Table 1. Combinatorial register allocation approaches ordered chronologically: technique, scope, spilling (SP), register assignment (RA), coalescing (CO), load-store optimization (LO), register packing (RP), live range splitting (LS), rematerialization (RM), multi-allocation (MA), size of largest problem solved optimally (SZ) in input instructions, and whether it is demonstrated to generate executable code (EX).

| approach              | technique | scope  | SP           | RA           | CO | LO           | RP           | LS | RM           | MA           | SZ          | EX           |

|-----------------------|-----------|--------|--------------|--------------|----|--------------|--------------|----|--------------|--------------|-------------|--------------|

| Goodwin et al. [46]   | IP        | global | ✓            | ✓            | ✓  | ✓            | ✓            | ✓  | ✓            | ✓            | ~ 2000      | ✓            |

| Appel et al. [3]      | IP        | global | ✓            |              |    | ✓            |              | ✓  |              |              | $\sim 2000$ | ✓            |

| Scholz et al. [85]    | PBQP      | global | ✓            | ✓            | ✓  |              | $\checkmark$ |    | $\checkmark$ |              | ~ 180       | $\checkmark$ |

| Nandivada et al. [73] | IP        | global | ✓            | $\checkmark$ |    | ✓            |              | ✓  |              |              | ?           | ✓            |

| Koes et al. [57]      | IP        | global | ✓            | ✓            |    | ✓            |              | ✓  | ✓            |              | ?           | ✓            |

| Barik et al. [8]      | IP        | global | $\checkmark$ | $\checkmark$ |    | $\checkmark$ | $\checkmark$ | ✓  | $\checkmark$ |              | 302         |              |

| Ebner et al. [35]     | IP        | global | ✓            |              |    | ✓            |              | ✓  |              |              | ?           | $\checkmark$ |

| Falk et al. [38]      | IP        | global | ✓            | $\checkmark$ |    | ✓            |              | ✓  |              | $\checkmark$ | ~ 1000      | ✓            |

| Colombet et al. [31]  | IP        | global | ✓            |              |    | ✓            |              | ✓  | ✓            | $\checkmark$ | ?           | $\checkmark$ |

#### 3 RELATED APPROACHES

This section provides an overview of combinatorial approaches to register allocation and instruction scheduling. The overview is complemented by more specific discussions in the rest of the paper. A more comprehensive review is provided by Castañeda Lozano and Schulte [24].

Combinatorial register allocation. Combinatorial approaches to register allocation in isolation (Table 1) have been proposed that satisfy all properties required to be practical: they model most or all of the standard program transformations (completeness, columns SP-MA), scale to medium-sized problems (scalability, column SZ), and generate executable code (executability, column EX). Furthermore, their ability to accommodate specific architectural features and alternative optimization objectives has been demonstrated in numerous studies [8, 38, 72, 73]. A particular focus has been to study the trade-off between solution quality and scalability. Numerous approaches [3, 31, 35] advocate solving spilling first (including relevant aspects of coalescing in the case of Colombet et al. [31]), followed by register assignment and coalescing. This arrangement can improve scalability with virtually no performance loss for single-issue and out-of-order processors, but is less suitable when register assignment and coalescing have high impact on code quality, such as in code size optimization [58] or in speed optimization for VLIW processors [31].

Combinatorial instruction scheduling. A large number of combinatorial instruction scheduling approaches have been proposed, where the underlying resource-constrained project scheduling problem has already been solved with IP in the early 1960s [13, 68, 96]. *Practical* approaches have been proposed for both local [86] and global [7, 103] instruction scheduling. Other approaches that scale to medium-sized problems but do not demonstrate executable code have been proposed for local [67, 100] and superblock [66] instruction scheduling. A detailed review of combinatorial instruction scheduling is provided by Castañeda Lozano and Schulte [24].

Combinatorial register allocation and instruction scheduling. Integrated combinatorial approaches (Table 2) capture the interdependencies between register allocation and instruction scheduling in a single combinatorial model. They typically are less scalable but can deliver better solutions than isolated approaches. A particular focus has been on VLIW processors, for which the interdependencies between both problems are strong [55]. As Table 2 shows, our integrated approach is the first that matches the practicality of isolated register allocation approaches. This concerns the program transformations modeled (completeness, columns SP-MA), the scalability (column SZ),

Table 2. Combinatorial register allocation and instruction scheduling approaches ordered chronologically: technique, scope, spilling (SP), register assignment (RA), coalescing (CO), load-store optimization (LO), register packing (RP), live range splitting (LS), rematerialization (RM), multi-allocation (MA), instruction selection (SE), size of largest problem solved optimally (SZ) in input instructions, and whether it is demonstrated to generate executable code (EX).

| approach                | technique | scope      | SP           | RA | CO | LO           | RP | LS           | RM | MA           | SE           | SZ   | EX |

|-------------------------|-----------|------------|--------------|----|----|--------------|----|--------------|----|--------------|--------------|------|----|

| Wilson et al. [101]     | IP        | global     | ✓            | ✓  | ✓  |              |    | ✓            |    |              | ✓            | 30   |    |

| Gebotys [41]            | IP        | local      | $\checkmark$ | ✓  |    | $\checkmark$ |    | ✓            |    |              | $\checkmark$ | 108  |    |

| Chang et al. [26]       | IP        | local      | $\checkmark$ |    |    | ✓            |    |              |    |              |              | ~ 10 |    |

| Bashford et al. [9]     | CP        | local      | $\checkmark$ | ✓  | ✓  | ✓            |    | ✓            |    |              | $\checkmark$ | 23   |    |

| Kästner [54]            | IP        | superblock |              | ✓  |    |              |    |              |    |              |              | 39   |    |

| Kessler et al. [56]     | DP        | local      |              |    |    |              |    | ✓            |    | ✓            | $\checkmark$ | 42   |    |

| Nagarakatte et al. [71] | IP        | loop       | $\checkmark$ | ✓  |    | ✓            |    | ✓            |    | $\checkmark$ |              | ?    |    |

| Eriksson et al. [37]    | IP        | loop       | $\checkmark$ |    |    | ✓            |    | ✓            |    | ✓            | $\checkmark$ | 100  |    |

| (this paper)            | CP        | global     | $\checkmark$ | ✓  | ✓  | $\checkmark$ | ✓  | $\checkmark$ | ✓  | ✓            |              | 946  | ✓  |

and the *executability* (column **EX**). While earlier integrated approaches might be able to generate executable code, this fact is not demonstrated in the respective publications, which precludes an evaluation of their practical significance. Moreover, only the approach by Wilson *et al.* [101] models register allocation at the global scope.

A particularly challenging problem not addressed by this paper is to incorporate instruction selection (column SE). The complexity of instruction selection and its interdependencies with register allocation and instruction scheduling are well-understood [50]. However, the potential benefits and scalability challenges of incorporating instruction selection into our integrated approach have not yet been explored.

Optimization techniques. IP is the most widely used optimization technique with the exception of Scholz and Eckstein [85] using PBQP, Bashford and Leupers [9] using CP, and Kessler and Bednarski [56] using DP. For combinatorial instruction scheduling in isolation a broader set of techniques has been applied, including the use of special-purpose branch-and-bound techniques [24].

# 4 LOCAL REGISTER ALLOCATION

This section introduces the combinatorial model for local register allocation and its underlying program transformations. The model is introduced step-by-step: starting from a definition of the input programs (Section 4.1) and register assignment (Section 4.2), the model is extended with alternative instructions (Section 4.3); spilling, live range splitting, and coalescing (Section 4.4); and rematerialization (Section 4.5). Section 4.6 briefly summarizes the main contributions in the model and program representation.

In the remainder of the paper, each variable added to the model is numbered by (Vn) where n is a number. Likewise, constraints are numbered by (Cn), where n is either a number or a period-separated number pair in case the constraint has been refined or extended.

# 4.1 Program Representation

The model for local register allocation is parameterized with respect to the input program and processor. This section defines the basic program parameters that describe an input program. Processor parameters and the remaining program parameters are introduced as needed.

- (a) Program representation.

- (b) Live ranges.

- (c) Register assignment.

Fig. 4. Local register assignment for the *loop* basic block from Example 2.

The input program consists of a sequence of operations in a single basic block. A key idea in the program representation is that it distinguishes between *operations* and *instructions* as well as between *operands* and *temporaries* to make the model more powerful. Operations are seen as abstract instructions (such as addition) that are implemented by specific processor instructions (such as add). Distinguishing between operations and instructions enables supporting alternative instructions, see Section 4.3. Operations contain *operands* that denote particular use and definition points of temporaries. Distinguishing between operands and temporaries enables register allocation transformations beyond register assignment and packing, as Sections 4.4 and 4.5 show.

Live-in (live-out) temporaries in a basic block are defined (used) by an entry (exit) operation, corresponding to the virtual instructions discussed in Section 2.1. This ensures that the live range of a temporary can be derived simply from the operations defining and using the temporary. An operation using or defining a temporary t is called a *user* respectively the *definer* of t.

Programs in this representation are described by a set of operations O, operands P, and temporaries T. An operation implemented by instruction i that uses temporaries  $t_1$  to  $t_n$  and defines temporaries  $t_{n+1}$  to  $t_m$  through its corresponding operands is represented as

$$p_{n+1}:t_{n+1},\ldots,p_m:t_m \leftarrow i \ p_1:t_1,\ldots,p_n:t_n.$$

The temporary used or defined by each operand p is denoted as temp(p). For simplicity, operand identifiers  $p_1, p_2, \ldots, p_m$  are omitted if possible.

As the input program is assumed to be in SSA, each temporary is defined exactly once. The program point immediately after the single definition of a temporary t is denoted as start(t), whereas the program point immediately before the last use of t is denoted as end(t). In our setup, the live range of a temporary t is indeed a range (or interval) (start(t), end(t)), and can be enforced straightforwardly in single basic blocks by local value numbering [32]. Live ranges being simple intervals is essential for modeling register assignment as Section 4.2 shows.

**Example 3.** Figure 4a illustrates the input representation of the *loop* basic block from Example 2 for local register allocation. Operand identifiers are omitted for simplicity. The live-in temporaries n and f are defined by an entry operation. The redefinitions of f (by mul) and n (by sub) are renamed as f' and n' to enforce SSA. Single definitions result in interval live ranges as shown in Figure 4b. The live-out temporaries n' and f' are used by an exit operation.

## 4.2 Register Assignment

This section introduces a simple model for register assignment, where temporaries are mapped to individual registers. The mapping is modeled by a variable  $\mathbf{reg}(t)$  for each temporary t giving its assigned register from a register set R. This paper uses symbolic domains for clarity; the actual

model maps symbolic values to integer values:

$$\operatorname{reg}(t) \in R \quad \forall t \in T.$$

(V1)

Register assignment is constrained by interference among temporaries. For example, n and f in Figure 4a interfere and therefore cannot be assigned to the same register. Register assignment and interference are captured by a simple geometric interpretation that can be modeled by global constraints. This interpretation, based on Pereira and Palsberg's *puzzle solving* approach [77], projects the register assignment of a basic block onto a rectangular area, where the horizontal dimension corresponds to an ordering of R (called *register array*) and the vertical dimension corresponds to program points. Each temporary t yields a rectangle of width(t) = 1, where the top and bottom borders correspond to the start(t) and end(t) program points of t's live range and the left border corresponds to the register reg(t) to which t is assigned. The direct mapping from temporaries to rectangles is possible due to the interval shape of the temporary live ranges. In this interpretation, the rectangles of interfering temporaries overlap vertically. A single *no-overlap* constraint in the model ensures that interfering temporaries are assigned to different registers:

no-overlap

$$(\{\langle \mathbf{reg}(t), \mathbf{reg}(t) + width(t), start(t), end(t)\} : t \in T\})$$

. (C1)

**Example 4.** Figure 4c shows the geometric interpretation of a register assignment for the *loop* basic block where n and n' are assigned to R0 and f and f' are assigned to R1. Assuming the program points are numbered from one to five, the corresponding instantiation of constraint C1 becomes no-overlap ( $\{\langle \mathbf{reg}(f), \mathbf{reg}(f) + 1, 1, 2 \rangle, \langle \mathbf{reg}(f'), \mathbf{reg}(f') + 1, 2, 5 \rangle, \langle \mathbf{reg}(n), \mathbf{reg}(n) + 1, 1, 3 \rangle, \langle \mathbf{reg}(n'), \mathbf{reg}(n') + 1, 3, 5 \rangle\}$ ).

Register packing. Register packing assigns temporaries of small bit-widths to different parts of larger-width registers to improve register utilization. This program transformation can be easily accommodated within the geometric representation of local register assignment. The registers in R are decomposed into their underlying register atoms (minimum register parts addressable by instructions), the function width(t) is extended to give the number of adjacent atoms that temporary t occupies, and the variable  $\mathbf{reg}(t)$  is reinterpreted as the leftmost atom to which t is assigned. This extension generalizes the geometric representation as a rectangle packing problem with rectangles of different widths and heights, which is precisely captured by constraint C1 as is.

Fig. 5. Reg. packing.

**Example 5.** Figure 5 illustrates register packing for a version of the *loop* basic block in Example 3 where f and f' have a width of 64 rather than 32 bits. Hexagon's register atoms (R0, R1, ...) have a width of 32 bits and can be combined into 64-bit registers (R1:0, R3:2, ...), hence width(f) = width(f') = 2. In the example register packing, f and f' are assigned to the combined register R1:0. This is modeled by the assignment of the variables reg(f) and reg(f') to R0, the leftmost atom of R1:0. n' and n' are assigned to R2.

*Pre-assignments.* As discussed in Section 2.1, an operand p might be pre-assigned to a certain register r (given by  $p \triangleright r$ ). Temporaries used or defined by such operands are pre-assigned to the corresponding registers:

$$\mathbf{reg}(temp(p)) = r \quad \forall p \in P : p \triangleright r. \tag{C2}$$

Register classes. Register files tend to be irregular in that different instructions are allowed to access different subsets of the available registers. A subset of the registers available to a particular instruction or group of instructions is called a *register class*. The processor parameter class(p) gives

the register class of operand *p*. The registers to which a temporary can be assigned are determined by the operands that define and use the temporary:

$$reg(temp(p)) \in class(p) \quad \forall p \in P.$$

(C3)

Section 4.4 below exploits register classes for spilling, where memory is treated as an additional register class, albeit with an unlimited number of registers.

Contributions. This section contributes a novel use of Pereira and Palsberg's register assignment and packing approach [77], by incorporating it into a combinatorial model. This is possible as constraint programming readily provides efficient solving methods for rectangle packing in the form of dedicated propagation algorithms for the *no-overlap* constraint. Integer programming, an alternative technique that is popular for register allocation (see Table 1), has difficulties in dealing with the disjunctive nature of rectangle packing [63].

#### 4.3 Alternative Instructions

The model is extended by *alternative instructions* that can be selected to implement operations relevant for register allocation. For example, ARM's Thumb-2 instruction set extension allows 16- and 32-bit instructions to be freely mixed, where the 16-bit instructions reduce code size but can only access a subset of the registers. The selection of 16- or 32-bit instructions is interdependent with register allocation as it has a significant effect on register pressure [36]. Alternative instructions are also central to model spilling, live range splitting, and coalescing as Section 4.4 explains.

The model supports alternative instructions as follows. The set of instructions that can implement an operation o is given by the parameter instrs(o), and the function class(p, i) is redefined to give the register class of operand p if implemented by instruction i. An operation that can be implemented by alternative instructions  $i_1, \ldots, i_n$  is represented as  $\cdots \leftarrow \{i_1, \ldots, i_n\}$   $\cdots$ .

A variable ins(o) for each operation o gives the instruction that implements o:

$$ins(o) \in instrs(o) \quad \forall o \in O.$$

(V2)

The register class of each operand p is linked to the instruction that implements p's operation in constraint C3 (changes to constraint C3 are highlighted in gray):

$$reg(temp(p)) \in class[p, ins(operation(p))] \quad \forall p \in P$$

(C3.1)

where the parameter operation(p) gives the operation of operand p. Multi-dimensional array access and set membership can be expressed with element constraints as described in Section 2.4.

# 4.4 Spilling, Live Range Splitting, and Coalescing

Spilling (allocate temporaries into memory, including load-store optimization and multi-allocation), live range splitting (allocate temporaries to different locations along their live ranges), and coalescing (assign copied temporaries to the same register) are supported by a single extension of the program representation and the model. The extension is based on the notion of optional copy operations.

A copy operation  $t_d \leftarrow \{i_1, \ldots, i_n\}$   $t_s$  defines a destination temporary  $t_d$  with the value of a source temporary  $t_s$  using a copy instruction among a set of alternatives  $\{i_1, \ldots, i_n\}$ . Another operation using  $t_s$  in the original program might after the introduction of the copy use  $t_d$  as an alternative, because  $t_s$  and  $t_d$  hold the same value as they are *copy-related*. If some operation uses  $t_d$ , the temporary is considered *live* and its definer copy operation *active*. Otherwise,  $t_d$  is considered *dead* and its definer copy operation *inactive*, effectively coalescing  $t_d$  into  $t_s$ . Inactive operations and dead temporaries do not affect the constraints in which they occur. Copy operations can be: implemented by store and load instructions to support spilling; implemented by register-to-register move instructions to support live range splitting; or made inactive to support coalescing.

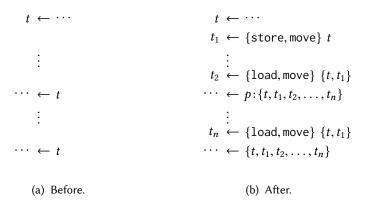

Fig. 6. Copy extension.

To handle store and load instructions and register-to-register move instructions uniformly, the register array is extended with a *memory* register class containing an unbound number of registers  $\{M0, M1, \ldots\}$  corresponding to memory locations in the function's stack frame. Unifying registers and memory yields a simple and expressive model that internalizes spilling by reducing register allocation to register assignment, where the register assigned to a temporary t implies t's allocation.

Copy extension. The number, type, and relation among the copy operations with which a program is extended to support spilling and live range splitting depends on the targeted processor architecture. This paper assumes load-store processors where values can be copied between registers and memory by single instructions. However, the model supports more complex architectures such as clustered VLIW processors by introducing additional copy operations.

For load-store processor architectures, a program is extended by visiting each temporary t once and introducing a *store-move* copy operation with instructions store and move at the program point immediately after the definition of t and a *load-move* copy operation with instructions load and move at the program point immediately before each use of t. The store-move can only use t, each load-move might use t or the destination temporary of the store-move, and each original user of t might use t or any of the introduced temporaries. Figure 6 illustrates the transformation.

Note that copy extension suggests the use of some alternative temporaries at points where they are not yet defined, for example  $t_n$  used by operand p in Figure 6. Such uses are invalid in isolated register allocation where operations are totally ordered. However, they become relevant in the integration with instruction scheduling (see Section 7), where operations (including copy operations) can be rearranged.

*Model extension.* The new decisions that follow from the introduction of copy operations are captured by three classes of variables. A variable temp(p) for each operand p gives the temporary that is used or defined by operand p among a set of copy-related alternatives temps(p):

$$\mathbf{temp}(p) \in temps(p) \quad \forall p \in P; \tag{V3}$$

a Boolean variable **live**(t) indicates whether temporary t is live:

$$\mathbf{live}(t) \in \mathbb{B} \quad \forall t \in T; \tag{V4}$$

and a Boolean variable **active**(*o*) indicates whether operation *o* is active:

$$active(o) \in \mathbb{B} \quad \forall o \in O. \tag{V5}$$

As is common in constraint programming, we define the set  $\mathbb{B}$  as  $\{0,1\}$  and abbreviate, for example, active(o) = 1 as active(o) and active(o) = 0 as  $\neg active(o)$ .

For uniformity, temp(p) is defined for both use and define operands even though no alternative is available for the latter. Similarly, active(o) is defined for both copy and non-copy operations even though the latter must always be active:

$$active(o) \quad \forall o \in O : \neg cop y(o). \tag{C4}$$

For a live temporary t, the definer of t and at least one user of t must be active:

live(t)

$$\iff$$

active(operation(definer(t)))

$\iff \exists p \in users(t) : active(operation(p)) \land temp(p) = t \quad \forall t \in T,$

(C5)

where definer(t) and users(t) are the operand(s) that might define and use a temporary t, and operation(p) is the operation of operand p.

With the introduction of alternative temporaries, the temporary used or defined by operands involved in pre-assignments becomes variable:

$$\mathbf{reg} \ [\mathbf{temp}(p)] = r \quad \forall p \in P : p \triangleright r \tag{C2.1}$$

Additionally, the register class constraint only needs to consider active operations:

reg [temp(p)]

$$\in class[p, ins(operation(p))] \quad \forall p \in P : active(operation(p))$$

. (C3.2)

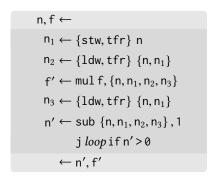

**Example 6.** Figure 7 illustrates the application of copy extension to support different implementations of spilling for the running example. Figure 7a shows the result of applying copy extension to n using Hexagon's store (stw), load (ldw), and register-to-register move (tfr) instructions.

Figure 7b illustrates the spill of n on the register array extended with memory registers. n is stored directly after its definition (copied to  $n_1$  which is assigned to memory register M0) and loaded before each use as  $n_2$  and  $n_3$  in a spill-everywhere fashion. This illustrates how the approach supports multi-allocation: immediately before mul,  $n_1$  and  $n_2$  are live simultaneously in memory (M0) and in a processor register (R0), simulating multiple allocations of their original temporary n.

Figure 7c illustrates the spill of n where load-store optimization is applied, rendering the second load-move inactive. Load-store optimization is only possible due to the availability of  $n_2$  as an alternative use for sub.

Live range splitting is supported similarly to spilling. For example, the live range of n can be split by implementing the copy operations that are active in Figure 7c with tfr instructions, and letting constraint C3.2 force the assignment of  $n_1$  and  $n_2$  to processor registers.

Discussion. The local register allocation model introduced in this section is the first to exploit copy operations, copy extension, and memory registers as a uniform abstraction to capture spilling, live range splitting, coalescing, and rematerialization (to be explained in Section 4.5). Only the related approaches of Wilson *et al.* [101, 102] and Chang *et al.* [26] extend the program representation with explicit copy operations and treat them exactly as original program operations. However, they do not model memory and processor registers uniformly, which requires special treatment of spilling and hence results in a more complicated model.

Alternative temporaries are related to Colombet *et al.*'s *local equivalence classes* [31] in their definition and targeted program transformations, and to Wilson *et al.*'s *alternative implementations* [101, 102] in their way of extending the original program representation with implementation choices to be considered by a solver.

Copy extension for load-store processors (Figure 6) allows a temporary's live range to be split at each definition and use point. Introducing even more splitting choices at other program points

- (a) Copy extension of n.

- (b) Spill-everywhere.

- (c) Load-store optimization.

Fig. 7. Copy extension and spilling for n in the *loop* basic block.

might enable better code. The number of these choices and their distribution among program points differs considerably among combinatorial register allocation approaches. This ranges from no live range splitting (as in Scholz and Eckstein [85]) to *split-everywhere* at every program point (as introduced by Appel and George [3]). The potential loss in code quality by bounding live range splitting to definition and use points is not yet established. In any case, the potential loss is mitigated as the model is expanded to global register allocation in Section 5 (where temporaries can be split at the boundaries of each basic block) and integrated with instruction scheduling in Section 7 (where the copy operations performing the splits can be rearranged).

## 4.5 Rematerialization

Rematerialization recomputes values at their use points rather than spilling them if the recomputation instructions are sufficiently cheap. A common case is rematerialization of *never-killed* values [25] that can be recomputed by a single instruction from operands that are always available. Typical examples are numeric constants and variable addresses in the stack frame. This paper captures rematerialization of never-killed values by a simple adjustment of copy extension and the register array and does not require any changes to the actual model. The level of rematerialization is similar to that of related approaches in Table 1.

Rematerializable temporaries are identified using the data-flow analysis of Briggs  $et\ al.\ [14]$ . The register array is extended with a rematerialization register class containing an unbounded number of registers (RM0, RM1, . . .). Rematerialization of a temporary t is modeled as if t were defined in a rematerialization register by a virtual instruction remat and loaded into a processor register by t's actual definer. This is achieved by adjusting the copy extension of each rematerializable temporary t to include the virtual instruction remat as an alternative to t's original definer instruction i, and include i as an alternative to the instructions of each load-move. Figure 8 illustrates this adjustment.

Modeling rematerialization as an alternative load-move instruction is inspired by Colombet *et al.* [31]. Unlike Colombet *et al.*, we use copy operations and extend the register array to avoid additional variables and constraints.

## 4.6 Summary

This section has introduced a program representation and model that enable all transformations offered by local, state-of-the-art register allocation using few variables and constraints. The compact,

Fig. 8. Adjusted copy extension for a rematerializable temporary.

yet expressive model is based on two significant contributions to the state of the art in combinatorial register allocation. First, the model incorporates Pereira and Palsberg's register assignment and packing approach [77] into a combinatorial setup. Second, it introduces copy operations, copy extension, and memory registers as a uniform abstraction to model spilling, live range splitting, coalescing, and rematerialization.

# 5 GLOBAL REGISTER ALLOCATION

This section extends the model from local to global register allocation for entire functions.

# 5.1 Program Representation

Global register allocation represents an input function as a set of basic blocks B where each basic block is defined as in Section 4.1. For a basic block b,  $O_b$  is the set of operations in b and  $T_b$  is the set of temporaries in b. The disjoint unions of these sets are denoted as O and T.

The input function is assumed to be in *linear static single assignment (LSSA)* form. LSSA generalizes SSA by enforcing that each temporary is defined once and only used within the basic block where it is defined [2, 5]. LSSA construction decomposes each temporary t with a live range spanning multiple blocks  $b_1, b_2, \ldots, b_n$  into a set of *congruent* temporaries  $t_{b_1} \equiv t_{b_2} \equiv \cdots \equiv t_{b_n}$ , where each temporary is local to its respective basic block. Hence the congruences denote that two or more temporaries originate from the same temporary and must therefore be assigned the same register. Live-in (live-out) temporaries resulting from LSSA construction are defined (used) by entry (exit) operations. The conventional form [92] of LSSA is assumed, where replacing all congruent temporaries by a single representative preserves the program semantics. LSSA is also referred to as the really-crude approach to SSA [2, 5] and maximal SSA [15]. LSSA's single definitions and local temporaries are crucial for modeling global register allocation: these properties preserve live ranges as simple intervals, which is required for modeling register assignment and packing geometrically.

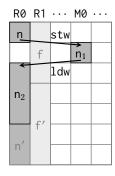

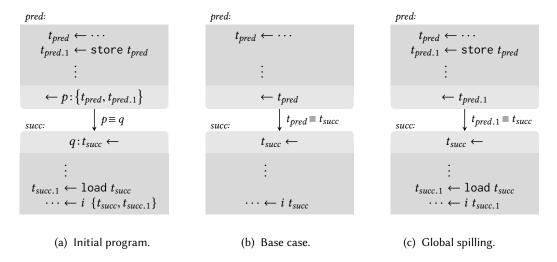

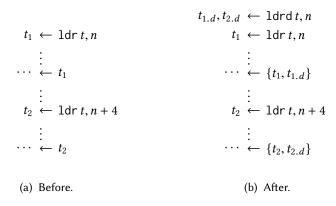

After LSSA construction, each basic block in the input function is copy-extended and adjusted for rematerialization as in Section 4. Copy extension induces alternative temporaries that can be used by each operation, making it necessary to lift the LSSA congruence from temporaries to operands as illustrated in Figure 9. Assume that pred and succ are adjacent basic blocks. After copy extension, each congruence  $t_{pred} \equiv t_{succ}$  is lifted to the congruence  $p_{pred} \equiv p_{succ}$  where  $p_{pred}$  is the exit operand using  $t_{pred}$  (or any of its alternatives  $t_{pred,1}, \ldots, t_{pred,n}$ ) and  $p_{succ}$  is the entry operand defining  $t_{succ}$ .

Fig. 9. Lifting of the LSSA congruence from temporaries to operands.

Fig. 10. CFG of the factorial function from Example 2 in LSSA where  $f_e$  is copy-extended.

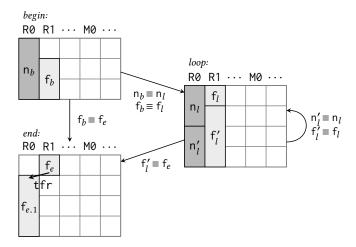

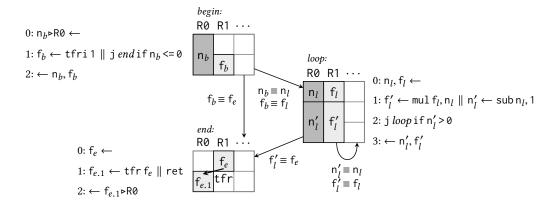

**Example 7.** Figure 10 shows the input representation of the factorial function from Example 2 for global register allocation. The function is in LSSA: each original temporary t in Example 2 is decomposed into a temporary  $t_b$  for each block b in which the temporary is live. For example, the temporary n is decomposed into temporaries  $n_b$  for the begin basic block and  $n_l$  for the loop basic block (for conciseness, only the first letter of a block name is used as index). To enforce single definitions, the redefinition of  $n_l$  is further renamed as  $n_l'$  similarly to Example 3. The resulting temporaries are local and defined only once. For example,  $n_l$  is defined once by the entry operation of loop and only used locally by mul and sub.

The input representation to global register allocation assumes that all temporaries are copy-extended, but the example limits copy extension to  $f_e$  for simplicity, which yields the alternative temporaries  $f_{e.1}$  and  $f_{e.2}$ . Also for simplicity, the LSSA congruence (displayed on the CFG arcs) is defined on temporaries and not on operands as shown in Figure 9.

## 5.2 Model

The program representation for global register allocation preserves the structure of the local model of each basic block described in Section 4 since operations, operands, and temporaries are local and basic blocks are only related by operand congruences. Therefore, a global model of register allocation is simply composed of the variables and constraints of each local model and linked with

Fig. 11. Interplay of live temporary, register class, and congruence constraints.

constraints that assign congruent operands to the same register:

$$\operatorname{reg}[\operatorname{temp}(p)] = \operatorname{reg}[\operatorname{temp}(q)] \quad \forall p, q \in P : p \equiv q.$$

(C6)

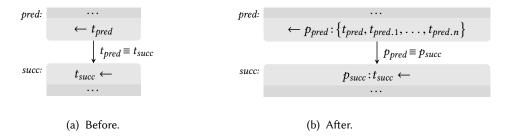

The congruence constraints extend the scope of all register allocation transformations to whole functions by propagating the impact of local decisions across basic blocks. Figure 11 illustrates the interplay of live temporary (C5), register class (C3.2), and congruence (C6) constraints across two basic blocks *pred* and *succ*.

Figure 11a displays a program fragment where the original temporary t is live across the boundaries of *pred* and *succ*. Temporary t is decomposed into  $t_{pred}$  and  $t_{succ}$  and copy-extended with a store-move copy operation (store) at *pred* and a load-move copy operation (load) at *succ* (the remaining copy operations and register-to-register move instructions are omitted for simplicity).

Figure 11b shows the base case where  $t_{pred}$  is not spilled (hence the store-move is deactivated). Since  $t_{pred.1}$  is dead, the exit operation of pred uses  $t_{pred}$  and the congruence constraints propagate the processor register of  $t_{pred}$  to  $t_{succ}$ . Now the processor register of  $t_{succ}$  is incompatible with the register class of load, which deactivates the load-move and forces i to use  $t_{succ}$ .

Figure 11c shows the global spill of t where the store-move is active and the exit operation of pred uses  $t_{pred.1}$  instead of  $t_{pred}$ . In this case the congruence constraints propagate the memory register of  $t_{pred.1}$  to  $t_{succ}$ , which forces i to use the temporary  $t_{succ.1}$  copied from  $t_{succ}$  by the load-move.

In general, entry and exit operations define and use multiple temporaries. All temporaries used or defined by the same boundary operation interfere and are thus necessarily assigned to different registers according to constraint C1.1. The use of LSSA in its conventional form [92] guarantees the absence of conflicts between this and the congruence constraints (C6).

The same rectangle assignment and packing constraint defined for a single basic block in Section 4.2 is used for each basic block:

no-overlap

$$(\{\langle \mathbf{reg}(t), \mathbf{reg}(t) + width(t), \mathbf{start}(t), \mathbf{end}(t)\} : t \in T_b \land \mathbf{live}(t)\}) \quad \forall b \in B$$

. (C1.1)

**Example 8.** Figure 12 illustrates global register allocation for the input function from Example 7. It corresponds to the better solution in the introductory Example 1: the temporaries derived from n are assigned to R0 and the temporaries derived from f are assigned to R1 with the exception of  $f_{e,1}$ .

Fig. 12. Global register allocation for the factorial function from Example 7.

$f_{e.1}$  is copied to R0 in the *end* basic block by activating its defining store-move and implementing it with the tfr instruction. The load-move of  $f_e$  is inactive, which renders  $f_{e.2}$  dead (C5).

The congruence constraints (C6) guarantee the compatibility of the local register assignments across boundaries. For example, the live-out temporaries of  $begin(\langle n_b, f_b \rangle)$  and the live-in temporaries of  $loop(\langle n_l, f_l \rangle)$  are pairwise congruent and thus assigned to the same registers ( $\langle R0, R1 \rangle$ ).

Discussion. The introduced model is the first to exploit the properties of LSSA for register allocation. LSSA and similar representations have been used to establish theoretical connections between programming paradigms [2], as an intermediate form in SSA construction [5], and as a basis for intermediate-level program analysis and optimization [40].

The model has a limitation in that it does not support multi-allocation across basic blocks. This is due to the fact that only one temporary among possibly many copied temporaries can be used by exit operands as seen in Figure 9. This limitation is shared with most combinatorial register allocation approaches (see Table 1), and its impact on scalability and code quality is unclear. Among integrated approaches (Table 2), only Wilson *et al.*'s model [101] is global. Wilson *et al.* propose a similar concept to congruence constraints but their model does not support multi-allocation.

Multi-allocation in a combinatorial setup is discussed in detail by Colombet *et al.* [31]. Among the three scenarios discussed by Colombet *et al.*, our model supports the optimizations illustrated in Figures 1 and 2 from Colombet *et al.*'s paper [31] but not in Figure 3.

## 6 INSTRUCTION SCHEDULING

This section describes the model for local instruction scheduling. It is mostly based on previous work on constraint-based scheduling by Malik *et al.* [67] and serves as an intermediate step towards the integrated register allocation and instruction scheduling model. It captures pre-register allocation scheduling and assumes the same basic block representation as in Section 4, with the only difference that operations are not totally ordered. Post-register allocation scheduling can be easily captured by introducing additional dependencies caused by register assignment.

*Variables.* Instruction scheduling assigns issue cycles to operations in a basic block such that dependencies between operations and processor resource constraints are satisfied. In the model, a

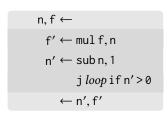

$$0: n, f \leftarrow \\ 2 \downarrow 1: f' \leftarrow \text{mul } f, n \parallel n' \leftarrow \text{sub } n, 1 \\ 2: j \text{ loop } if n' > 0 \\ 3: \leftarrow n', f'$$

$$1: f' \leftarrow \text{mul } f, n \parallel n' \leftarrow \text{sub } n, 1 \\ 2: j \text{ loop } if n' > 0$$

$$3: \leftarrow \text{units used}$$

(a) Schedule.

(b) Cumulative usage of slots.

Fig. 13. Instruction schedule for the loop basic block from Example 3.

variable **issue**(*o*) defines the cycle in which *o* is issued relative to the beginning of the basic block:

$$issue(o) \in \mathbb{N}_0 \quad \forall o \in O. \tag{V6}$$

Dependency constraints. Valid schedules must preserve the input order among dependent operations. An operation u depends on another operation d if u uses a temporary t defined by d. If operation d is issued at cycle issue(d), its result becomes available at cycle issue(d) + lat(ins(d)), where ins(o) is the instruction that implements operation o and lat(i) is the latency of instruction i. To satisfy the dependency, u must be issued after the result of d is available, that is:  $issue(u) \ge issue(d) + lat(ins(d))$ . The model includes one such inequality for each use of a temporary t, where u uses t through operand t and t defines t through operand t:

**issue**(operation(q)) ≥ **issue**(operation(p)) + lat(ins(operation(p)))

$$\forall t \in T, \forall p \in \{definer(t)\}, \forall q \in users(t) : temp(q) = t.$$

(C7)

The dependency constraints deviate slightly from early constraint models such as that of Malik *et al.* [67] in that they make the underlying uses and definitions of temporaries explicit. This is essential for the integration with register allocation as explained in Section 7. The integration also requires that the virtual entry instruction is given a latency of one. This requirement ensures that live-in temporaries in a basic block have non-empty live ranges and are thus assigned to different registers according to constraint C1.1.

*Processor resource constraints.* The capacity of processor resources such as functional units and buses cannot be exceeded. As discussed in Section 2.3, this paper assumes a set of processor resources S where each resource  $s \in S$  has a capacity cap(s) and each instruction i consumes con(i, s) units of each resource s during dur(i, s) cycles. The model includes a *cumulative* constraint for each resource s to ensure that the capacity of s is never exceeded by the scheduled operations:

cumulative

$$(\{(\mathbf{issue}(o), dur(ins(o), s), con(ins(o), s)\}) : o \in O\}, cap(s)) \quad \forall s \in S.$$

(C8)

This paper assumes that resource consumption always starts at the issue of the consumer. The model can be easily extended to capture more complex scenarios (for example, modeling each stage in a processor pipeline) by adding an offset off(i, s) to the issue cycle of the consumer (**issue**(o)) in the resource constraint (C8) [19].

**Example 9.** Figure 13a shows a schedule of the *loop* basic block from Example 3 where all instructions are assumed to have a latency of one cycle. The vertical dimension ranges over cycles as opposed to program points in register allocation.

Hexagon is a VLIW processor that allows up to four instructions to be issued in parallel. In the example, only mul and sub can be issued in parallel ( $\parallel$ ) as they do not depend on each other. The multiple-issue capacity of Hexagon is modeled as a resource slots with cap(slots) =

4, con(i, slots) = 1, and dur(i, slots) = 1 for each instruction  $i \in \{mul, sub, j if\}$ . With this resource, constraint C8 is instantiated as cumulative ( $\{\langle issue(mul), 1, 1 \rangle, \langle issue(sub), 1, 1 \rangle, \langle issue(j if), 1, 1 \rangle\}$ , 4). Figure 13b shows the cumulative usage of the slots resource over time. The figure shows that parallelism in the example is not limited by the slots resource constraint (C8) but by the dependency constraint  $issue(j if) \geq issue(sub) + 1$  over temporary n'(C7).

Discussion. Constraint programming is a popular technique for resource-constrained scheduling problems [6], as it provides efficient and dedicated propagation algorithms for scheduling constraints. As shown here, it enables a simple model using a single variable per operation and a single constraint for each dependency and resource. For comparison, integer programming typically requires a decomposition into n variables with  $\{0,1\}$  domain for each operation and n linear constraints for each resource, where n is an upper bound on the number of issue cycles of the basic block. This decomposition limits the scalability of approaches based on integer programming [24].

#### 7 GLOBAL REGISTER ALLOCATION AND INSTRUCTION SCHEDULING

This section combines the models for global register allocation and instruction scheduling into an integrated model that precisely captures their interdependencies. The integrated model is a significant contribution to combinatorial code generation as, for the first time, it captures the same program transformations as state-of-the-art heuristic approaches (see Table 2).

The model assumes the program representation described in Section 5.1, except that operations within basic blocks are not totally ordered. The model uses the variables and constraints from the global register allocation model and the instruction scheduling model generalized to handle copy-extended programs. This generalization allows copy operations (introduced to support spilling, live range splitting, and rematerialization) to be scheduled in the same manner as the original program operations, by means of issue cycle variables. Compared to the register allocation model without instruction scheduling, the ability to schedule and thus rearrange copy operations increases the freedom of their supported program transformations.

Live ranges and issue cycles. In the integrated model, live ranges link register allocation and instruction scheduling since they relate registers assigned to temporaries with the issue cycles of their definers and users. The live start of a temporary t is linked to the issue of the operation d defining t, and the live end is linked to the issue of the last operation  $u_n$  using t as shown in Figure 14. Variables  $\mathbf{start}(t)$  and

issue

$$(u_1)$$

$$\vdots$$

issue $(u_n)$

$$t$$

$$\vdots$$

$$t$$

$$\vdots$$

$$\vdots$$

$$end(t)$$

Fig. 14. Live range of t.

end(t) are introduced for each temporary t giving its live start and end cycles:

$$\mathbf{start}(t), \mathbf{end}(t) \in \mathbb{N}_0 \quad \forall t \in T.$$

(V7)

The live start of a (live) temporary *t* corresponds to the issue of its defining operation:

$$\mathbf{start}(t) = \mathbf{issue}(operation(definer(t))) \quad \forall t \in T : \mathbf{live}(t),$$

(C9)

while the live end of *t* corresponds to the issue of the last user operation:

$$\mathbf{end}(t) = \max_{p \in users(t): \mathbf{temp}(p) = t} \mathbf{issue}(operation(p)) \quad \forall t \in T: \mathbf{live}(t).$$

(C10)

Generalized instruction scheduling. The generalized model captures alternative instructions, optional (active or inactive) operations, and alternative temporaries. Alternative instructions are handled by using the variable ins(o) instead of the parameter ins(o) for each operation o. The generalized dependency constraints handle inactive operations and alternative temporaries by making each dependency involving an operation that potentially uses temporary t through

Fig. 15. Integrated solution for the factorial function from Example 7.

operand q conditional on whether the operation is active and actually uses t:

$$issue(operation(q)) ≥ issue(operation(p)) + lat [ins(operation(p))]$$

$$∀t ∈ T, ∀p ∈ {definer(t)}, ∀q ∈ users(t) : active(operation(q)) ∧ temp(q) = t.$$

(C7.1)

The generalized processor resource constraints handle optional operations by making their resource usage conditional on whether they are active. Additionally, they are extended to global scope by including a *cumulative* constraint for each resource *s* and basic block *b*:

cumulative

$$\left(\left\{\left\langle \mathbf{issue}(o), dur \left[\mathbf{ins}(o), s\right], con \left[\mathbf{ins}(o), s\right]\right\rangle : o \in O_b \land \mathbf{active}(o)\right\}, cap(s)\right)$$

$$\forall b \in B, \forall s \in S.$$

(C8.1)

**Example 10.** Figure 15 shows a solution to the integrated register allocation and instruction scheduling problem for the function in Example 7. The scheduled operations are shown besides the register assignment of each basic block. The memory registers M0,M1,... are omitted for conciseness. The solution corresponds to the faster assembly code given in Example 1. The final assembly code shown in Example 1 can be generated by simply removing the entry and exit virtual operations and replacing each temporary with its assigned register.